FPGA Günlükleri – 1 Bit Comparator

Bu yazı dizisinde sıfırdan FPGA öğrenen birinin notlarını, çalışmalarını, fikirlerini ve yaptığı hataları göreceksiniz. Ne kadar günlük düzeninde olur bilemiyorum fakat vakit buldukça bir şeyler karalamayı planlıyorum. Uzun zaman MCU kullanan biri olarak şunu söyleyebilirim ki temel Boolean cebirini ve bir takım dijital elektronik konularını unutmuşum. Bu yazılarda hem dijital elektroniğin temellerini hemde FPGA yapısını ele alarak düzenli bir takım çalışmalar yapacağım. Bu işe 1 Bitlik karşılaştırıcı tasarlayarak başlayalım.

Bu yazı dizisinde sıfırdan FPGA öğrenen birinin notlarını, çalışmalarını, fikirlerini ve yaptığı hataları göreceksiniz. Ne kadar günlük düzeninde olur bilemiyorum fakat vakit buldukça bir şeyler karalamayı planlıyorum. Uzun zaman MCU kullanan biri olarak şunu söyleyebilirim ki temel Boolean cebirini ve bir takım dijital elektronik konularını unutmuşum. Bu yazılarda hem dijital elektroniğin temellerini hemde FPGA yapısını ele alarak düzenli bir takım çalışmalar yapacağım. Bu işe 1 Bitlik karşılaştırıcı tasarlayarak başlayalım.

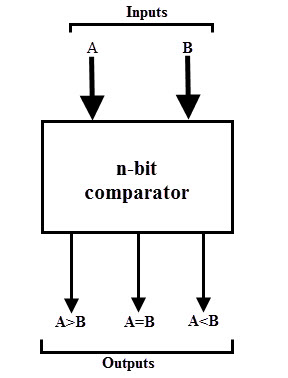

Comparator yani Karşılaştırıcılar bize girilen değerlerin kıyaslanması sonucu bir takım çıkış sinyalleri veren yapılardır. Bu çıktılar fark karşılaştırma referanslarına göre değişebilir. Biz bu yapıda sayıların büyüklüğünü karşılaştıran bir Comparator tasarlayacağız. Buna aynı zamanda “Magnitude Comparator” de diyebiliriz.

Yapısı :

Yapının kaç bitlik olduğu tamamen keyfidir. Biz ilk uygulama için 1-Bit olanını yapalım. Bu mantıkla siz n-Bit olanını çalışmanıza göre tasarlayabilirsiniz. Bu tarz lojik devreleri tasarlamak için Karnaugh haritası çıkarmamız gerekiyor. Karnaugh haritasının nasıl çıkarıldığını bilmiyorsanız önce bunun öğrenin, zira bunu da anlatacak olursak yazı çok uzun olur.

İncelenecek 3 adet durum var. Bir karşılaştırma işleminde A ve B giriş değerleri olmak üzere

- Durum : A < B

- Durum : A > B

- Durum : A = B

Olarak tanımlanır. Buradan her bir çıkış için ayrı Karnaugh haritaları oluşturup ona göre devreyi tasarlarız. Yapacağımız karşılaştırıcı 1 Bit olduğu için bu kolay olacak.

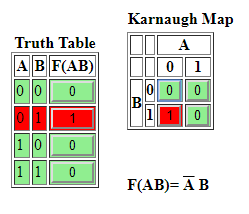

1.Durum için A < B yani A = 0 ve B = 1 için bir çıkış almak istiyoruz başka türlü A < B durumu elde edilemez. Karnaugh haritasını şu şekilde olacak.

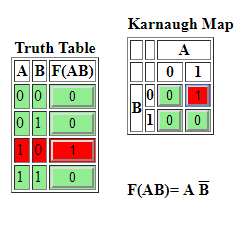

2. Durum için A > B yani A = 1 ve B = 0 için çıkış alacağız. Elde edeceğimiz tek A > B durumu bu olacaktır. Karnaugh haritasını şu şekilde olacak.

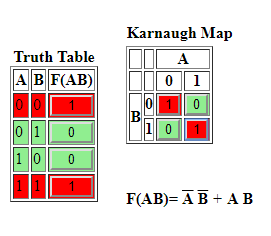

Son durumda ise A = B yani 2 adet durum ile sağlanan bu koşul A = 0 ve B = 0 ile birlikte A = 1 ve B = 1 durumlarıdır. Bu yapı biraz tanıdık gelebilir. Buna Exclusive-NOR denir. Haritası bu şekildedir.

Artık bu 3 durumu ayrı çıkışlara yönlendirerek tasarımı tamamlayabiliriz. Bunu FPGA ortamında VHDL kullanarak şu şekilde basitçe ifade edebiliyoruz.

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 |

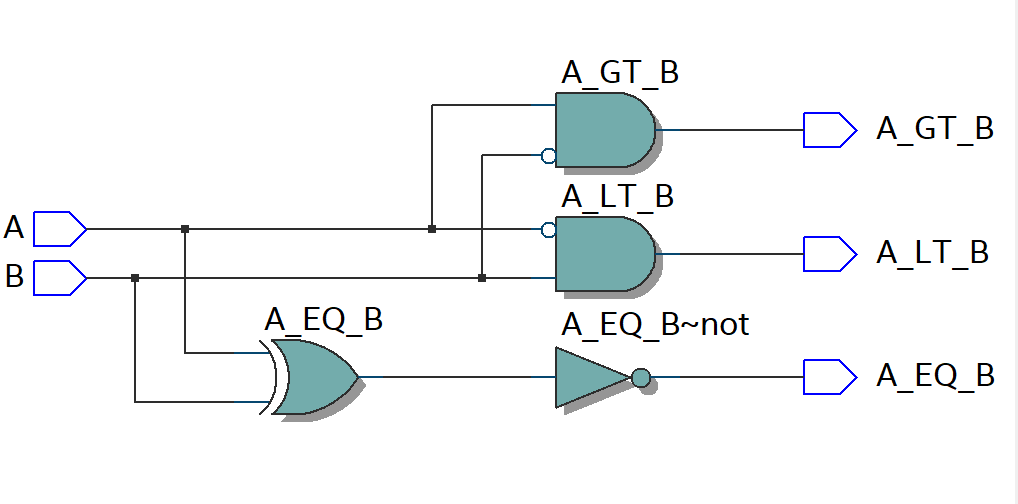

library IEEE; use IEEE.STD_LOGIC_1164.all; entity Comparator_1Bit is port ( A : in STD_LOGIC; B : in STD_LOGIC; A_LT_B : out STD_LOGIC; A_GT_B : out STD_LOGIC; A_EQ_B : out STD_LOGIC ); end Comparator_1Bit; architecture karakter of Comparator_1Bit is begin A_LT_B <= (not(A) and B); A_GT_B <= (A and not(B)); A_EQ_B <= (A xnor B); end karakter; |

Tanımlamalarda kullandığım isimlerin açıklaması

- A_LT_B = A Lower Than B

- A_GT_B = A Greater Than B

- A_EQ_B = A Equal B

RTL çıktısı ise şu şekilde olacak.

Umarım açıklayıcı olmuştur. Bir başka yazıda görüşmek üzere.

Esen kalın.

Bu FPGA ‘a bulaşmak istemiyordum ama dayanamadım okudum.mükemmel bir anlatım.Teşekkürler.

Ben teşekkür ederim Kudret ağabey. 🙂